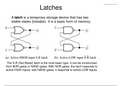

Latches

A latch is a temporary storage device that has two

stable states (bistable). It is a basic form of memory.

The S-R (Set-Reset) latch is the most basic type. It can be constructed

from NOR gates or NAND gates. With NOR gates, the latch responds to

active-HIGH inputs; with NAND gates, it responds to active-LOW inputs.

, Latches

The active-HIGH S-R latch is in a stable (latched) condition

when both inputs are LOW.

0 R 1

0

Assume the latch is initially RESET Q

(Q = 0) and the inputs are at their Latch

inactive level (0). To SET the latch initially

(Q = 1), a momentary HIGH signal RESET

0

1

is applied to the S input while the R Q

0 S

remains LOW.

0 R 1

0

To RESET the latch (Q = 0), a Q

momentary HIGH signal is Latch

applied to the R input while the S initially

remains LOW. SET

1

0

Q

0 S

, Latches

The active-LOW S-R latch is in a stable (latched) condition

when both inputs are HIGH.

Assume the latch is initially RESET 1 S 1

0

Q

(Q = 0) and the inputs are at their

Latch

inactive level (1). To SET the latch initially

(Q = 1), a momentary LOW signal RESET

is applied to the S input while the R 1

0

1 R Q

remains HIGH.

To RESET the latch a momentary 1 S 1

0

Q

LOW is applied to the R input

Latch

while S is HIGH. initially

Never apply an active set and 1 SET

0

Q

reset at the same time (invalid). 1R

, Latches

A latch is a temporary storage device that has two

stable states (bistable). It is a basic form of memory.

The S-R (Set-Reset) latch is the most basic type. It can be constructed

from NOR gates or NAND gates. With NOR gates, the latch responds to

active-HIGH inputs; with NAND gates, it responds to active-LOW inputs.

, Latches

The active-HIGH S-R latch is in a stable (latched) condition

when both inputs are LOW.

0 R 1

0

Assume the latch is initially RESET Q

(Q = 0) and the inputs are at their Latch

inactive level (0). To SET the latch initially

(Q = 1), a momentary HIGH signal RESET

0

1

is applied to the S input while the R Q

0 S

remains LOW.

0 R 1

0

To RESET the latch (Q = 0), a Q

momentary HIGH signal is Latch

applied to the R input while the S initially

remains LOW. SET

1

0

Q

0 S

, Latches

The active-LOW S-R latch is in a stable (latched) condition

when both inputs are HIGH.

Assume the latch is initially RESET 1 S 1

0

Q

(Q = 0) and the inputs are at their

Latch

inactive level (1). To SET the latch initially

(Q = 1), a momentary LOW signal RESET

is applied to the S input while the R 1

0

1 R Q

remains HIGH.

To RESET the latch a momentary 1 S 1

0

Q

LOW is applied to the R input

Latch

while S is HIGH. initially

Never apply an active set and 1 SET

0

Q

reset at the same time (invalid). 1R

, Latches